DISTRIBUTION STATEMENT — Distribution authorized to U.S. Government agencies only for administrative or operational use (effective date is date of this manual). Other requests for this document must be referred to San Antonio ALC/MMEDT, Kelly AFB, TX 78241-5000.

THIS MATERIAL MAY BE REPRODUCED BY OR FOR THE U.S. GOVERNMENT PURSUANT TO THE COPYRIGHT LICENSE UNDER THE (DFAR) CLAUSE AT 52.227-7013 (15 MAY 1987).

HANDLING AND DESTRUCTION NOTICE — Comply with distribution statement and destroy by any method that will prevent disclosure of contents or reconstruction of the document.

# 9132A-68030 MEMORY INTERFACE POD

## Instruction Manual

P/N 864736 March 1989 Rev. 1, 4/89 @1989 John Fluke Mfg. Co., Inc. All rights reserved. Litho in U.S.A.

#### WARRANTY

#### COVERAGE

Fluke warrants the 9132A-68030 Memory Interface Pod to be free from defects in material and workmanship under normal use and service for a period of one (1) year from the date of shipment. The warranty does not cover parts that connect directly to the Unit Under Test (flying lead sets, microprocessor sockets, clips, headers, and Sync Adapter assemblies). This warranty extends only to the original purchaser and does not apply to any product that has been misused, altered, or has been subjected to abnormal conditions of operation.

Fluke's obligations under this warranty are limited to repair or replacement of a product that is returned to an authorized Service Center within the warranty period, provided that we determine that the product is defective. If we determine that the failure has been caused by misuse, alteration, or abnormal conditions of operation, or if the warranty period has expired, we will repair the Pod and bill you for the reasonable repair cost.

#### **SERVICE**

If a failure occurs, send the product, postage prepaid, to the closest Service Center with a description of the difficulty. Repairs will be made or the product replaced, and it will be returned, transportation prepaid. Fluke assumes NO risk for damage in transit.

#### DISCLAIMER

THE FOREGOING WARRANTY IS EXCLUSIVE AND IN LIEU OF ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS, OR ADEQUACY FOR ANY PARTICULAR PURPOSE OR USE. FLUKE SHALL NOT BE LIABLE FOR ANY SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER IN CONTRACT, TORT, OR OTHERWISE.

#### **GETTING ANSWERS AND ADVICE**

To enhance your use of this Pod, Fluke will be happy to answer your questions about applications and use. Address all correspondence to: JOHN FLUKE MFG. CO., INC., P.O. BOX C9090, EVERETT, WASHINGTON 98206, ATTN: Sales Department.

JOHN FLUKE MFG. CO., INC., P.O. BOX C9090, EVERETT, WASHINGTON 98206

## **IMPORTANT NOTE**

Use of the 9132A Interface Pod requires that the 9100-Series Mainframe have software installed that is version 4.0 or later.

| • |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

## **Table of Contents**

| SECTION                                                                                                                             | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| 1 INTR                                                                                                                              | ODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-1                      |  |

| 1-1.<br>1-2.<br>1-3.<br>1-4.<br>1-5.<br>1-6.                                                                                        | PURPOSE OF THE INTERFACE POD                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-1<br>1-2<br>1-3<br>1-6 |  |

| 2 9132                                                                                                                              | A SETUP FOR 9100-SERIES MAINFRAMES                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1                      |  |

| 2-1.<br>2-2.<br>2-3.<br>2-4.<br>2-5.<br>2-6.<br>2-7.<br>2-8.<br>2-9.<br>2-10.<br>2-11.<br>2-12.<br>2-13.<br>2-14.<br>2-15.<br>2-16. | GETTING STARTED INSTALLING THE 68030 DATABASE INSTALLING PROCESSOR AND ROM SUPPORT Installing the Personality Module Installing the Sync Module Installing the ROM Module(s) Installing the RAM Modules(s) Closing the Pod Case CONNECTING THE POD TO THE MAINFRAME PERFORMING THE POD SELF TEST CONNECTING THE POD TO THE UUT POD SETUPS Interactive Setup and Calibration Saving and Restoring Pod Setups Setup for Relocated Boot ROM Address Space TROUBLESHOOTING HINTS |                          |  |

| 3 POD  3-1. 3-2. 3-3. 3-4.                                                                                                          | OPERATIONS WITH 9100-SERIES MAINFRAMES  INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-1<br>3-1<br>3-2<br>3-2 |  |

| 3-5.<br>3-6.<br>3-7.<br>3-8.<br>3-9.                                                                                                | Examples of Bus Test Operations and Fault Messages Using the Diagnose Bus Test Using the Stimulus Routines READ AND WRITE OPERATIONS Read Operations                                                                                                                                                                                                                                                                                                                         | 3-5<br>3-11<br>3-11      |  |

### TABLE OF CONTENTS, continued

| SECTION        | TITLE                                                                      | PAGE  |

|----------------|----------------------------------------------------------------------------|-------|

| 3-20.          | Write Operations                                                           | 3-18  |

| 3-30.          | TESTING THE UUT RAM                                                        | 3-21  |

| 3-31.          | RAM Fast Test                                                              | 3-22  |

| 3-32.          | RAM Full Test                                                              | 3-23  |

| 3-33.          | HyperRAM Test                                                              | 3-24  |

| 3-34.          | HyperRAM TestTESTING THE UUT ROM                                           | 3-26  |

| 3-35.          | Signature Gathering from UUT Boot ROMs                                     | 3-27  |

| 3-39.          | Signature Gathering from Other UUT ROMs                                    | 3-29  |

| 3-40.          | Signature Testing Obtaining a List of Signatures                           | 3-30  |

| 3-41.          | Obtaining a List of Signatures                                             | 3-30  |

| 3-42.          | Deleting a Signature File                                                  | 3_31  |

| 3-43.          | USING THE RUN UUT MODE                                                     | 3-31  |

| 3-44.          | RUN UUT Special                                                            | 3-32  |

| 3-45.          | RUN UUT Virtual                                                            | 3-32  |

| 3-46.          | USING BREAKPOINTS                                                          | 3-32  |

| 3-47.          | Enabling Breakpoints                                                       | 3_33  |

| 3-48.          | Setting the Break Address                                                  | 3-33  |

| 3-49.          | USING OVERLAY MEMORY                                                       | 3-34  |

| 3-50.          | Selecting Overlay Memory                                                   | 3-34  |

| 3-51.          | Selecting Overlay Memory                                                   | 3-35  |

| 3-52.          | PROBE AND SCOPE SYNCHRONIZATION MODES                                      | 3-35  |

| 3-53.          | Address Sync                                                               | 3-36  |

| 3-54.<br>3-55. | Data Sync                                                                  | 3-36  |

| 3-33.<br>3-56. | Free-Run Sync                                                              | 3-36  |

| 3-30.<br>3-57. | 68030 Pod Sync Timing Description and Suggestions                          | 3-37  |

| 3-57.<br>3-58. | INTERRUPTS                                                                 | 3-37  |

| 3-59.          | Communicating with Correspond                                              | 3-37  |

| 3-60.          | Communicating with Coprocessors                                            | 3-3/  |

| 3-61.          | Simulating Rreakpoint Acknowledge                                          | 3-39  |

| 3-62.          | Simulating Breakpoint Acknowledge USING THE 68030 CACHE BURST FILL MODE    | 3-39  |

| 3-63.          | The BURST_SZ Pod Setup Parameter Versus                                    |       |

| 2.4            | the 68030 Cache Burst Fill Mode                                            | 3-40  |

| 3-64.          | Enabling and Disabling the 68030 Cache Burst Fill Mode                     | 3-40  |

| 3-65.          | Adjusting the Pod Data Sync Timing during                                  |       |

| 2.66           | Adjusting the Pod Data Sync Timing during 68030 Cache Burst Fill Transfers | 3-41  |

| 3-66.          | INFORMATION ABOUT 68030 SIGNALS                                            | 3-41  |

| A UUT F        | ROM SUPPORT                                                                | A-1   |

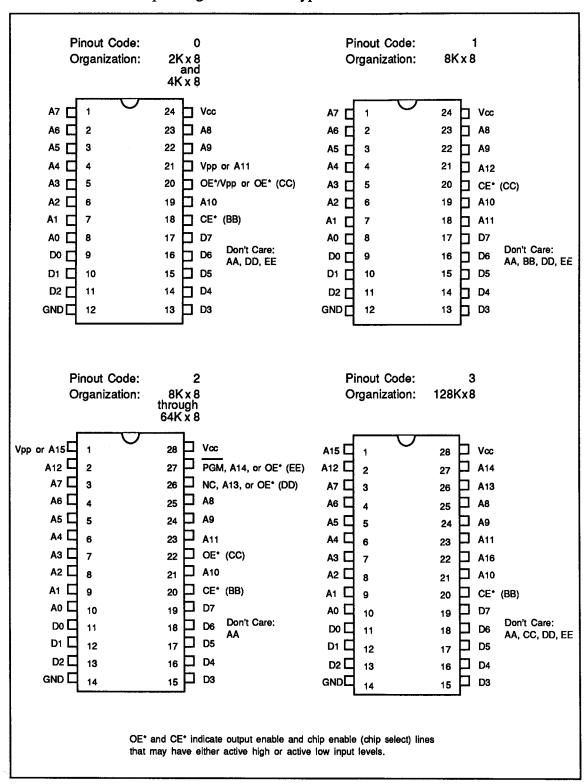

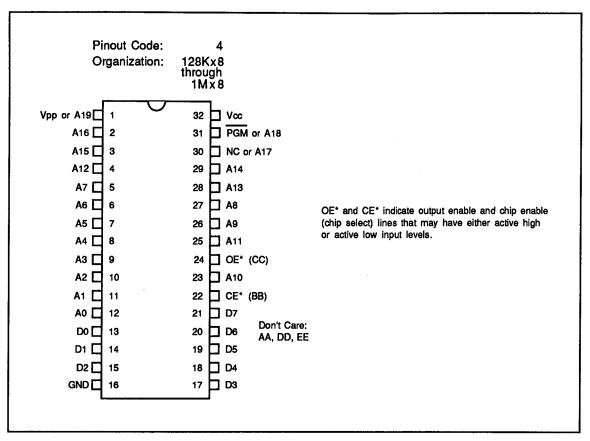

| A-1.           | ROM TYPES SUPPORTED BY THE 9132A                                           | A-1   |

| B PROB         | LEMS DUE TO A MARGINAL UUT                                                 | B-1   |

| B-1,           | INTRODUCTION                                                               | D 1   |

| B-2.           | UUT OPERATING SPEED AND MEMORY ACCESS                                      | D-I מ |

|                | UUT NOISE LEVELS                                                           | D 1   |

|                | BUS LOADING                                                                | R-1   |

### TABLE OF CONTENTS, continued

| SECTIO | N            | TITLE                                                  |        |  |  |  |

|--------|--------------|--------------------------------------------------------|--------|--|--|--|

|        | B-5.         | CLOCK LOADING                                          | B-1    |  |  |  |

| С      | TEST         | ING UUTS WITH SOLDERED-IN COMPONENTS                   | C-1    |  |  |  |

|        | C-1.         | INTRODUCTION                                           | C-1    |  |  |  |

|        | C-2.         | INTRODUCTION TESTING WITH A SOLDERED-IN MICROPROCESSOR | C-1    |  |  |  |

|        | C-3.         | TESTING WITH SOLDERED-IN ROMS                          | C-3    |  |  |  |

| D      | EXTE         | NDED POD SETUPS                                        | D-1    |  |  |  |

|        | D-1.         | SETUP AND CALIBRATION PARAMETERS                       | D-1    |  |  |  |

|        | D-2.         | SELECTING THE BUS CYCLE CLOCK SOURCE                   | D-5    |  |  |  |

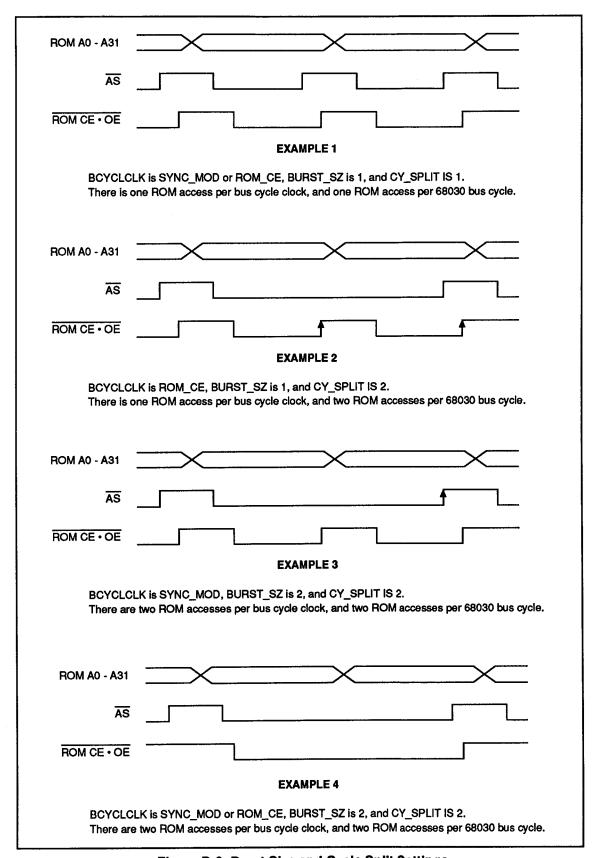

|        | D-3.         | SETTING THE BURST SIZE AND CYCLE SPLIT SETUPS.         | D-7    |  |  |  |

|        | D-4.         | USING THE 68030 ROM_BASE SETUP                         | D-8    |  |  |  |

|        | D-5.         | USING THE 68030 BRST_EN SETUP                          | D-8    |  |  |  |

|        | D-6.         | USING THE XFER_CAL SETUP                               |        |  |  |  |

| E      | USIN         | G THE 9132A POD FROM TL/1 PROGRAMS                     | E-1    |  |  |  |

|        | E-1.         | READING THE DATABASE VERSION NUMBER                    | E-1    |  |  |  |

|        | E-2.         | READING THE POD SOFTWARE VERSION NUMBER                | E-1    |  |  |  |

|        | E-3.<br>E-4. | TL/1 PROGRAMMING APPLICATIONS                          | E-1    |  |  |  |

|        | E-4.<br>E-5. | Pod Address Space Options                              | E-1    |  |  |  |

|        | E-6.         | Pod-Specific Setup InformationList of Pod Sync Modes   | E-Z    |  |  |  |

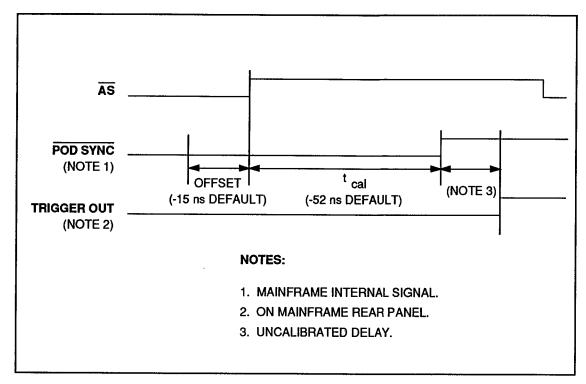

|        | E-7.         | Pod Sync Calibration Data                              | E-3    |  |  |  |

|        | E-8.         | Reserved Names in TL/1 Programs                        | F-7    |  |  |  |

|        | E-9.         | Available Bus Test TL/1 Support Programs               | E-7    |  |  |  |

|        | E-10.        | Other Available TL/1 Support Programs                  | E-14   |  |  |  |

|        | E-11.        | 9132A Pod Special Faults (pod_special)                 | E-18   |  |  |  |

|        | E-12.        | Bit Definitions of Fault Masks                         | E-21   |  |  |  |

|        | E-13.        | RUN UUT PROGRAM EXAMPLES                               | E-26   |  |  |  |

|        | E-14.        | POD VIRTUAL ADDRESSES                                  | E-26   |  |  |  |

| 4      | E-15.        | 68030 PART LIBRARY FOR GFI APPLICATIONS                | E-28   |  |  |  |

| F      | SELF         | TEST FAILURE CODES                                     | F-1    |  |  |  |

| G      | RESE         | T CONNECTION                                           | G-1    |  |  |  |

|        | G-1.         | INTRODUCTION                                           | G-1    |  |  |  |

|        | G-2.         | FUNCTIONAL TEST CONSIDERATIONS                         | G-1    |  |  |  |

|        | G-3.         | CONVENIENCE CONSIDERATIONS                             | G-1    |  |  |  |

|        | G-4.         | TEST CONDITIONS THAT CAUSE A RESET                     | G-2    |  |  |  |

| Н      | POD I        | BUS TEST FAULT COVERAGE                                | H-1    |  |  |  |

|        | H-1.         | INTRODUCTION                                           | H-1    |  |  |  |

|        | H-2.         | BUS TEST OPERATION                                     | H-1    |  |  |  |

| INDEX  | <b>&lt;</b>  | IN                                                     | IDEY_1 |  |  |  |

|  |  | ( ) |

|--|--|-----|

|  |  |     |

|  |  |     |

|  |  |     |

## **List of Tables**

| TABLE | TITLE                                                   | PAGE |

|-------|---------------------------------------------------------|------|

| 1-1.  | 9132A Memory Interface Pod Specifications               | 1-4  |

| 1-2.  | 9132A Ordering Information                              | 1-6  |

| 2-1.  | Sync Adapter Signals                                    | 2-11 |

| 3-1.  | Address Bits Checked for Breakpoints                    | 3-31 |

| 3-2.  | 68030 Signal Descriptions                               | 3-42 |

| 3-3.  | 68030 Microprocessor Pin Locations                      | 3-47 |

| A-1.  | ROM Types Similar to Standard ROMs                      | A-1  |

| A-2.  | Predefined ROM Codes                                    | A-4  |

| C-1.  | Connections Between the Pod and the UUT (68030)         | C-2  |

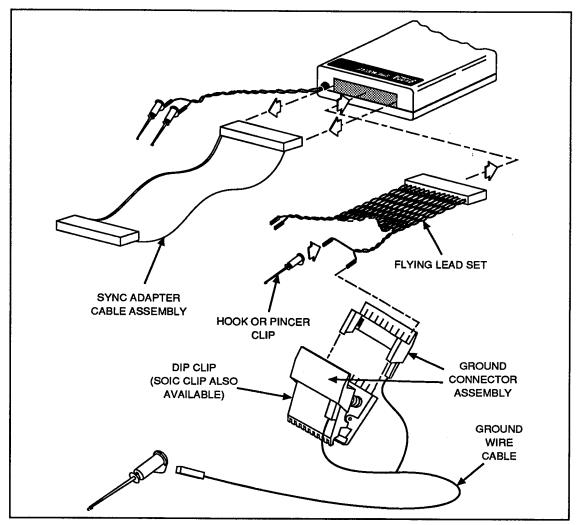

| C-2.  | Accessories for the Flying Lead Set                     | C-3  |

| D-1.  | Pod Setup and Calibration Parameters                    | D-1  |

| E-1.  | Pod Address Space Options                               | E-2  |

| E-2.  | 68030 Pod Setup Parameters                              | E-2  |

| E-3.  | 68030 Pod Sync Calibration Data                         | E-7  |

| E-4.  | Address Signal Mapping to Fault Masks                   | E-22 |

| E-5.  | Data Signal Mapping to Fault Masks                      | E-23 |

| E-6.  | Interrupt Signal Mapping to Fault Masks                 | E-23 |

| E-7.  | Miscellaneous Signal Mapping to Fault Masks             | E-24 |

| E-8.  | Control Signal Mapping to Fault Masks                   | E-24 |

| E-9.  | Forcing Signal Mapping to Fault Masks                   | E-25 |

| E-10. | Read and Write Virtual Addresses                        | E-26 |

| E-11. | RUN UUT Virtual Addresses                               | E-28 |

| F-1.  | Pod Self Test Failure Codes                             | F-1  |

| H-1.  | Fault Coverage for 68030 "test_bus" Version 1.1         | H-2  |

| H-2.  | Typical Side Effect Faults Reported by 68030 "test_bus" |      |

|       | Version 1.1                                             | H-3  |

|       |                                                         |      |

|  |  |   |  | <i></i> |

|--|--|---|--|---------|

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  | ( )     |

|  |  |   |  | \ /     |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  | • |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

|  |  |   |  |         |

## **List of Figures**

| FIGURE | TITLE                                                      | PAGE |

|--------|------------------------------------------------------------|------|

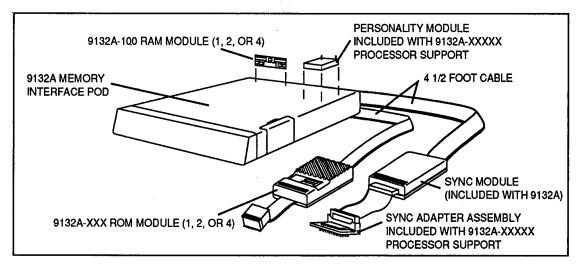

| 1-1.   | Components of a Standard 9132A Pod                         | 1-2  |

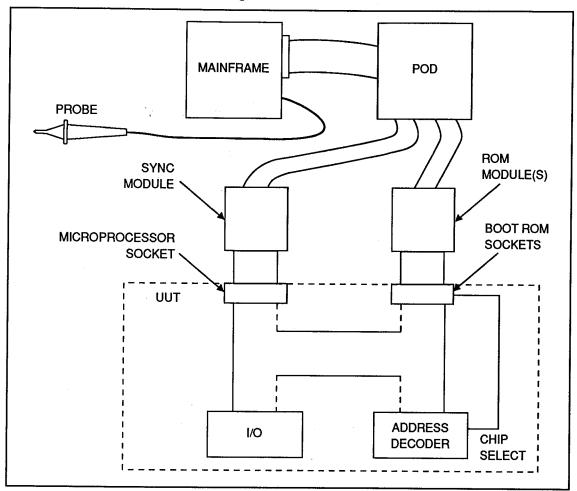

| 1-2.   | Communications Between the Mainframe, the Pod, and the UUT | 1-3  |

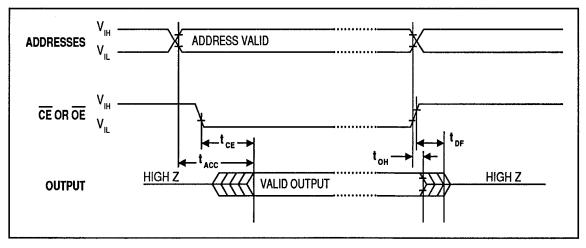

| 1-3.   | AC Waveforms                                               | 1-5  |

| 2-1.   | Opening the Back Panel of the Pod                          | 2-2  |

| 2-2.   | Installing the Personality Module                          | 2-2  |

| 2-3.   | Connection of the External Modules to the Interface Pod    | 2-3  |

| 2-4.   | Connecting the RAM Modules                                 | 2-4  |

| 2-5.   | Connection of the Interface Pod to the Mainframe           | 2-5  |

| 2-6.   | Connecting the ROM and Sync Modules to the Self Test PCA   |      |

| 2-7.   | Inserting UUT ROMs into the ROM Module                     | 2-8  |

| 2-8.   | Connecting the Sync Module to the UUT                      | 2-10 |

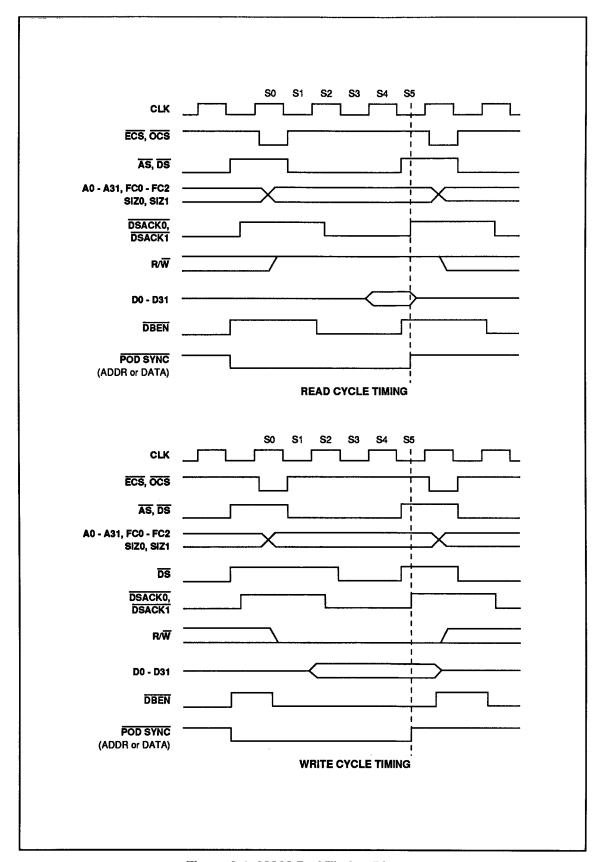

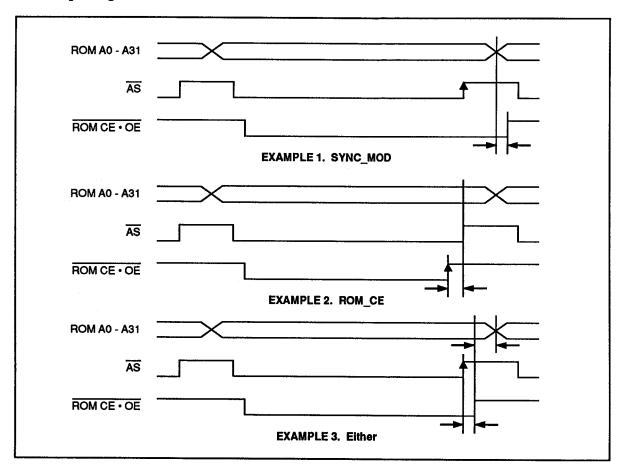

| 3-1.   | 68030 Pod Timing Diagram                                   | 3-38 |

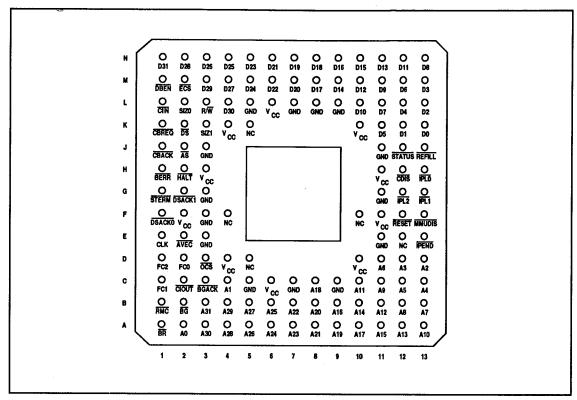

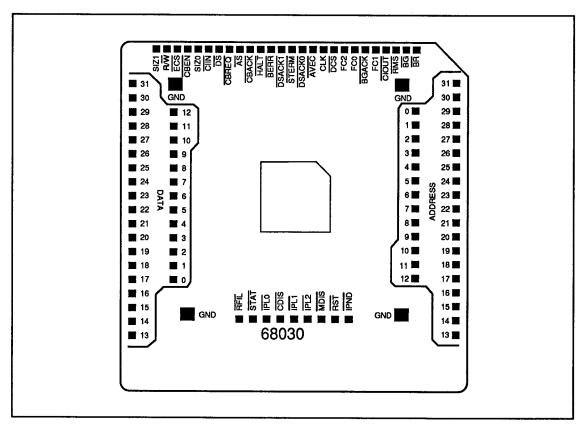

| 3-2.   | 68030 Microprocessor Pin Assignments (PGA Bottom View)     | 3-46 |

| 3-3.   | Signal Locations on the Sync Adapter Assembly              | 3-46 |

| A-1.   | Pin Diagrams of Supported ROM Types                        | A-2  |

| C-1.   | Installing the Flying Lead Set and Clip Accessories        | C-2  |

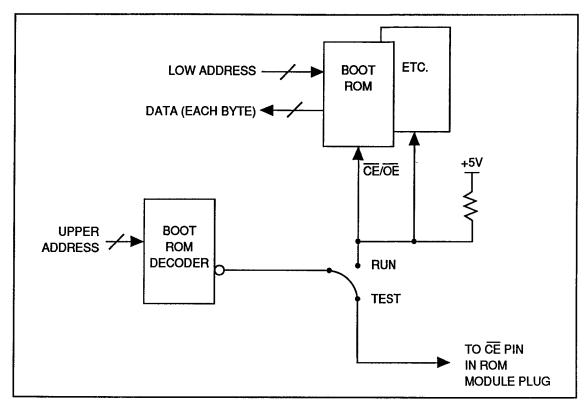

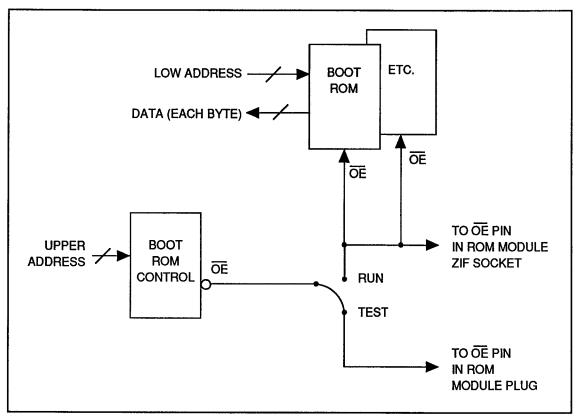

| C-2.   | Disabling the UUT Boot ROM                                 | C-4  |

| C-3.   | Testing the Fixtured UUT Boot ROM                          | C-4  |

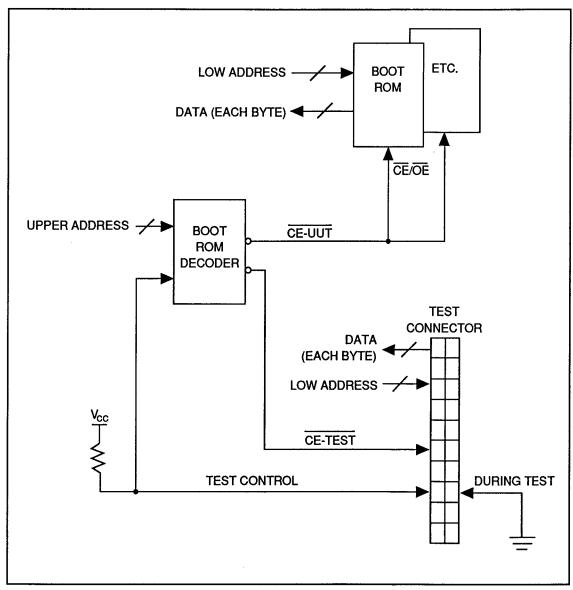

| C-4.   | Relocating the UUT Boot ROM Address Space                  | C-6  |

| D-1.   | BCYCLCLK Generation                                        | D-6  |

| D-2.   | Burst Size and Cycle Split Settings                        | D-0  |

| E-1.   | 68030 Pod Data Sync Mode Calibration                       | E-6  |

## Section 1 Introduction

#### PURPOSE OF THE INTERFACE POD

1-1.

The 9132A Memory Interface Pod allows you to use any Fluke 9100-Series Digital Test System/Station to troubleshoot equipment that uses a variety of microprocessors and ROMs.

The 9100-Series Digital Test System/Station (referred to hereafter as the Mainframe) is used to service printed circuit boards, instruments, and systems that use microprocessors and ROMs. The 9132A Memory Interface Pod (referred to as the Pod) replaces the boot (P)ROM in the unit under test (UUT) and serves both as an interface to allow the Mainframe access to components on the UUT and as an emulator of the UUT's ROMs.

In normal Mainframe/Pod operation, the Pod adapts the general-purpose architecture of the Mainframe to the specific pin layout of a variety of ROM and microprocessor types. By supplying instructions to the microprocessor through the ROM interface, the Pod gains complete access to devices on the UUT that are connected to the microprocessor's bus. In this troubleshooting mode, the Pod typically carries out a UUT read or write operation, and the Mainframe presents the results to the user. In the RUN UUT mode, the UUT microprocessor is connected through buffers to the UUT ROMs located in the ROM sockets on the ROM modules. The UUT executes the code in the UUT ROMs.

#### **NOTE**

It is assumed that the user of this manual is familiar with the basic operation of the 9100-Series Digital Test System/Station.

#### UNPACKING 1-2.

Unpack the 9132A and inspect each component for possible shipping damage. If the equipment is damaged or there are parts missing, contact your shipping agent or your Fluke sales representative immediately.

Save the original shipping box and any protective shipping devices, including foam packing. If repairs, equipment relocation, or extended storage are necessary, use the original foam-packed shipping containers to prevent unnecessary damage. If the original packaging is not available, order new containers from your Fluke sales representative.

#### PHYSICAL DESCRIPTION OF THE POD

The Pod connects to the Mainframe through a round shielded cable, and connects to the UUT through a set of ROM modules that are inserted into the UUT's boot ROM sockets. The UUT's ROMs are removed from the UUT and are replaced by the Pod's ROM modules. (The UUT's boot ROMs are placed in sockets located on the ROM modules.) In addition, a Sync Module is connected to various lines on the UUT to control timing and reset for the UUT processor. The components of a standard 9132A Interface Pod are shown in Figure 1-1. Figure 1-2 shows the communication between the Pod, the Mainframe, and the UUT.

The Pod consists of a base unit and several attached parts. One Sync Module and up to four ROM Modules may be attached to the Pod. The Pod contains the control software and supporting hardware that is required to do the following:

- Receive and execute commands from the Mainframe.

- Report UUT fault conditions to the Mainframe.

- Exercise the UUT.

Figure 1-1. Components of a Standard 9132A Pod

The Mainframe supplies operating power for the Pod. The UUT provides external timing signals required by the Pod, which allows the Pod to synchronize its internal functions to those of the UUT.

Overvoltage protection circuits or fuses on each line to the UUT guard against damage to the Pod that could result from the following:

- Incorrectly inserting a ROM Module cable plug into the UUT's boot ROM socket.

- UUT faults that place potentially damaging voltages on the lines to the UUT's boot ROM sockets.

#### **NOTE**

The overvoltage protection circuits guard against voltages of +12V to -7V on any one pin of the ROM Module plug. Multiple faults, especially of long duration, may cause Pod damage.

Figure 1-2. Communication Between the Mainframe, the Pod, and the UUT

A power-level sensing circuit monitors the voltage level of the UUT power supply. If UUT power drops below an acceptable level, the Pod notifies the Mainframe of a bad power supply condition.

A self-test socket on the Pod enables the Mainframe to check Pod operation. The ROM Module cable plugs and the Sync Adapter cable assembly are connected to the self-test socket during self test operation, which allows the Mainframe to investigate the Pod's internal functions.

#### **POD SPECIFICATIONS**

1-4.

Specifications for the Pod are listed in Table 1-1.

#### Table 1-1. 9132A Memory Interface Pod Specifications

| EMULATION SPEC                                                                                                                                                       | CIFICATIONS                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Boot ROM Sp                                                                                                                                                          | ace Size (See Appendix A)4K bytes min. |

| DC ELECTRICAL S                                                                                                                                                      | SPECIFICATIONS                         |

| Protection                                                                                                                                                           |                                        |

| ESD Protection on UUT According to Section UUT According to Section 1997. Improper Control Protection Float Voltage Mechanical in Pod Input Specifical Section 1997. | UUT Access Pin                         |

| Input High Vol<br>Input Leakage                                                                                                                                      | tage                                   |

| ROM Module                                                                                                                                                           | •                                      |

| Output Low Vo                                                                                                                                                        | oltage                                 |

|                                                                                                                                                                      | tput Specifications                    |

| Overdrive Out                                                                                                                                                        | puts (for UUT Reset):                  |

| Output High V                                                                                                                                                        | oltage                                 |

| AC ELECTRICAL S<br>(See Figure 1-3)                                                                                                                                  | SPECIFICATIONS                         |

| ROM Module                                                                                                                                                           |                                        |

| Access Time:                                                                                                                                                         |                                        |

| Slower of CE                                                                                                                                                         | nta                                    |

Table 1-1. 9132A Memory Interface Pod Specifications (cont)

###

Figure 1-3. AC Waveforms

#### CAUTION

Many UUTs relocate or alias the boot ROM address space from its normal base address of 0 to another base address. If this process takes place, the UUT must relocate or alias the entire contents of the boot ROM space to the new base address for the Pod to function properly.

This manual provides complete information for using the Pod, including installation, setup, and operating instructions. The summary below explains briefly what kind of information is available in each of the sections:

Section 1 Explains the purpose of the Memory Interface Pod and contains a general description of the Pod.

Section 2 Contains installation instructions for connecting the Pod to the Mainframe and the UUT. This section also contains a description of the built-in self test to ensure that the Pod is functioning correctly, and a setup function to tailor Pod operating characteristics to a UUT type.

Section 3 Describes how to set various functions that are specific to the processor on your UUT. Section 3 also describes the address structure of the Pod and lists the processor signals on your UUT.

Appendices Contains miscellaneous material that may prove valuable when using the Pod.

#### LIST OF REPLACEMENT COMPONENTS

1-6.

Because the plugs and clips associated with the 9132A can be attached and detached from the UUT many times, it is possible that pins on the plugs or the clip leads may break. Replacement components may be ordered from John Fluke Mfg. Co., Inc. or an authorized representative by using the Fluke order number. Table 1-2 contains ordering information for these parts.

Table 1-2. 9132A Ordering Information

| DESCRIPTION                                 | ORDER NUMBER |  |  |

|---------------------------------------------|--------------|--|--|

| Flying Lead Set                             | 777078       |  |  |

| Hook Clip                                   | 757500       |  |  |

| Pincer Clip                                 | 845409       |  |  |

| 24-pin Header                               | 845391       |  |  |

| 28-pin Header                               | 845388       |  |  |

| 32-pin Header                               | 845396       |  |  |

| 128-position PGA Socket                     | 854703       |  |  |

| 68030 Sync Adapter Cable Assembly           | 761684       |  |  |

| 68030 Sync Adapter Assembly                 | 863436       |  |  |

| 68030 Personality Module                    | 863456       |  |  |

| Fuse, .25 x 1.25, 0.25A, 250V, Fast (USA)   | 109314       |  |  |

| Fuse Holder Part, Cap, 5 x 20 mm (European) | 461020       |  |  |

#### 68030 SOCKET ADAPTER ACCESSORIES

1-7.

The Sync Adapter Assembly is designed to have the minimum size needed to connect to the UUT microprocessor socket. If you find it difficult to probe points around the microprocessor, consider using a socket adapter to raise the Sync Adapter Assembly (such as the CS128-72TG socket from Advanced Interconnections Corp.).

## static awareness

A Message From

John Fluke Mfg. Co., Inc.

Some semiconductors and custom IC's can be damaged by electrostatic discharge during handling. This notice explains how you can minimize the chances of destroying such devices by:

- 1. Knowing that there is a problem.

- 2. Learning the guidelines for handling them.

- 3. Using the procedures, and packaging and bench techniques that are recommended.

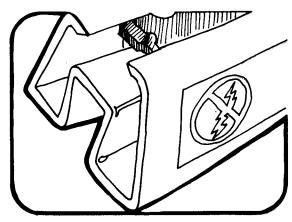

The Static Sensitive (S.S.) devices are identified in the Fluke technical manual parts list with the symbol " 🚫 "

The following practices should be followed to minimize damage to S.S. devices.

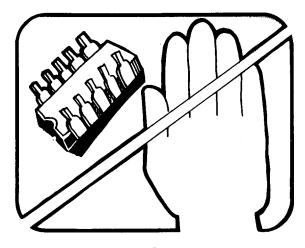

1. MINIMIZE HANDLING

2. KEEP PARTS IN ORIGINAL CONTAINERS UNTIL READY FOR USE.

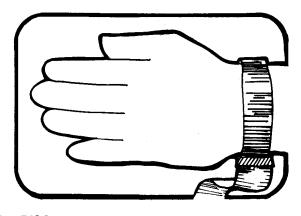

DISCHARGE PERSONAL STATIC BEFORE HANDLING DEVICES. USE A HIGH RESIS-TANCE GROUNDING WRIST STRAP.

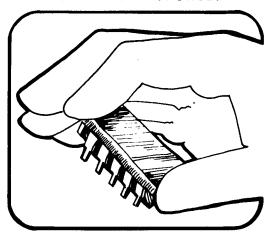

4. HANDLE S.S. DEVICES BY THE BODY

5. USE STATIC SHIELDING CONTAINERS FOR HANDLING AND TRANSPORT

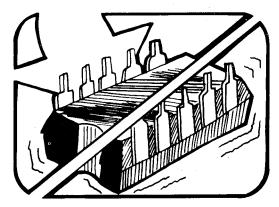

DO NOT SLIDE S.S. DEVICES OVER ANY SURFACE

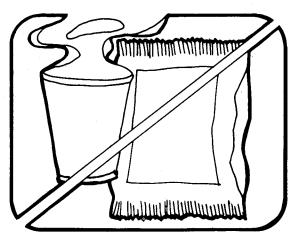

7. AVOID PLASTIC, VINYL AND STYROFOAM® IN WORK AREA

PORTIONS REPRINTED

WITH PERMISSION FROM TEKTRONIX, INC.

AND GENERAL DYNAMICS, POMONA DIV.

8. WHEN REMOVING PLUG-IN ASSEMBLIES, HANDLE ONLY BY NON-CONDUCTIVE EDGES AND NEVER TOUCH OPEN EDGE CONNECTOR EXCEPT AT STATIC-FREE WORK STATION. PLACING SHORTING STRIPS ON EDGE CONNECTOR HELPS TO PROTECT INSTALLED SS DEVICES.

- HANDLE S.S. DEVICES ONLY AT A STATIC-FREE WORK STATION

- 10. ONLY ANTI-STATIC TYPE SOLDER-SUCKERS SHOULD BE USED.

- 11. ONLY GROUNDED TIP SOLDERING IRONS SHOULD BE USED.

A complete line of static shielding bags and accessories is available from Fluke Parts Department, Telephone 800-526-4731 or write to:

JOHN FLUKE MFG. CO., INC. PARTS DEPT. M/S 86 9028 EVERGREEN WAY EVERETT, WA 98204

# 9132A Setup for 9100-Series Mainframes

#### **GETTING STARTED**

2-1.

This section contains setup and installation instructions for the Pod. These instructions show how to install processor support to test UUTs that use the 68030 processor and how to connect the external and internal modules that support your specific UUT. Once the Pod is connected to the Mainframe, perform the built-in self test to ensure that the Pod is operating correctly. After the Pod has passed the self test, you can connect the ROM and Sync Modules to the UUT, initialize the Pod and the UUT, and begin testing.

#### **INSTALLING THE 68030 DATABASE**

2-2.

The 68030 database for the 9100-Series Mainframe is contained on one 3.5-inch floppy disk supplied with the 9132A-68030.

To install the database on a Mainframe with a hard drive, insert the disk into the Mainframe floppy drive, press MAIN MENU on the keypad, press SOFT KEYS, then select COPY DISK FROM DR1 TO HDR and press ENTER. (The database only needs to be installed once.) Once the database is installed on the Mainframe, place the original floppy disk in a safe place in case it is needed in the future.

To use the database on a Mainframe with two floppy drives, first copy the database disk to a backup disk using the Mainframe COPY function. Remove the original from the floppy drive and insert the copy into the system USERDISK. Each time the Mainframe is reset the database is read from the floppy disk. Place the original floppy disk in a safe place in case it is needed in the future.

#### **INSTALLING PROCESSOR AND ROM SUPPORT**

2-3.

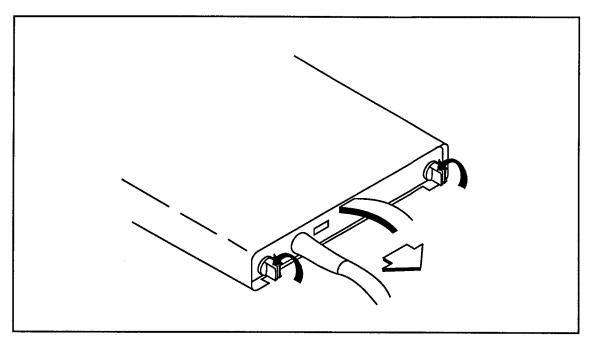

Before installing or changing the internal or external modules in the Pod, use the following steps to gain access to the module connectors inside the back panel of the Pod:

- 1. Check that the Mainframe power is OFF.

- 2. Open the back panel of the Pod by turning the thumbscrews on each side counterclockwise, and then pulling the panel out from the case (see Figure 2-1).

Figure 2-1. Opening the Back Panel of the Pod

#### **Installing the Personality Module**

2-4.

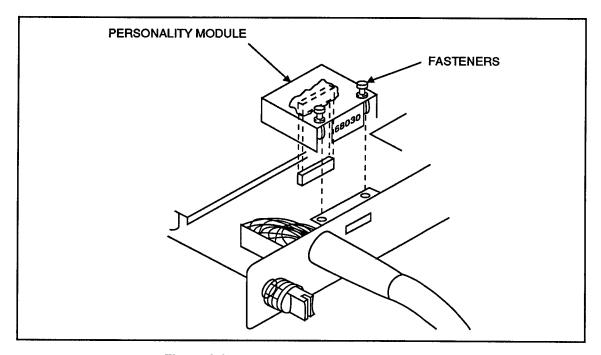

To configure the Pod for the 68030 processor, a 68030 Personality Module must be installed in the Pod. The following steps describe the procedure for installing the Personality Module:

1. Carefully plug the personality module in the connector on the left-hand side of the main printed circuit assembly (pca) as shown in Figure 2-2.

Figure 2-2. Installing the Personality Module

2. Push down on the fasteners on the back of the personality module to snap it into place. The processor type should show through the "Configured for" slot in the back panel.

#### Installing the Sync Module

2-5.

The following steps describe the procedure for installing the Sync Module into the Pod:

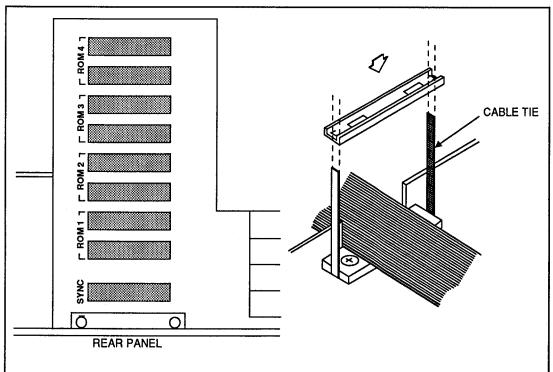

- 1. Plug the Sync Module cable into the connector labeled "SYNC" near the back of the main pca (as shown in Figure 2-3), making sure not to twist or kink the Sync Module cable.

- 2. After plugging in the Sync Module (and one or more ROM Modules), secure the cables by tightening the cable tie located on the back panel of the Pod.

#### Installing the ROM Module(s)

2-6.

The following steps describe the procedure for installing the ROM Module(s) into the Pod:

1. Plug the ROM Module(s) into the numbered connectors on the main pca (as shown in Figure 2-3), making sure not to twist or kink the ROM Module cables. If you are using one ROM Module, that module must be plugged into the sockets marked "ROM 1." If you are using two ROM Modules, the modules must be plugged into the sockets "ROM 1" for ROM Module number 1 and "ROM 2" for ROM Module number 2.

Figure 2-3. Connection of the External Modules to the Interface Pod

#### NOTE

To prevent confusion after the back of the Pod is closed, each of the ROM Modules should be numbered as you insert them into the ROM Module connectors. Stick one of the numbered labels (provided with the Pod) on the back of the UUT connector plug.

2. After plugging in the ROM Module(s) (and the Sync Module), secure the cables by tightening the cable tie located on the back panel of the Pod.

#### Installing the RAM Module(s)

2-7.

For each ROM Module that has been installed in the Pod, an equivalent number of RAM Modules must also be installed. (For convenience, the Pod operates correctly if more RAM Modules than ROM Modules are installed.)

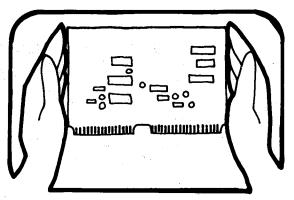

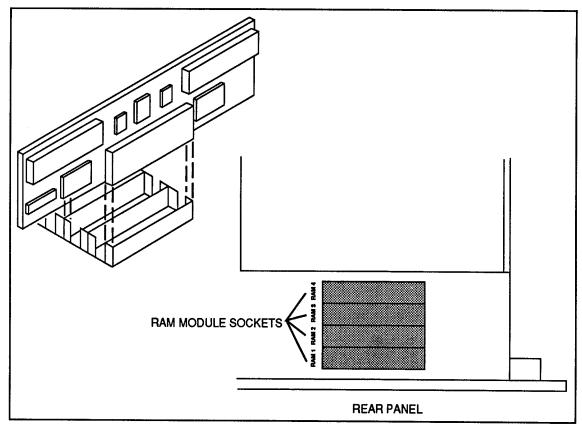

Plug the RAM Module(s) into the connectors on the right side of the main pca (as shown in Figure 2-4). If only one ROM Module has been installed, install only one RAM Module in the "RAM 1" connector. If two ROM Modules have been installed, install RAM Modules into "RAM 1" and "RAM 2" connectors. If four ROM Modules have been installed, install RAM Modules in all the RAM connectors.

Figure 2-4. Connecting the RAM Modules

After installing or changing the internal or external modules in the Pod, push the back panel back into the Pod case. Make sure the ROM Module and Sync Module cables are inserted properly into the slot on the top of the panel. Tighten the thumbscrews by pressing them in and turning clockwise.

#### CONNECTING THE POD TO THE MAINFRAME

2-9.

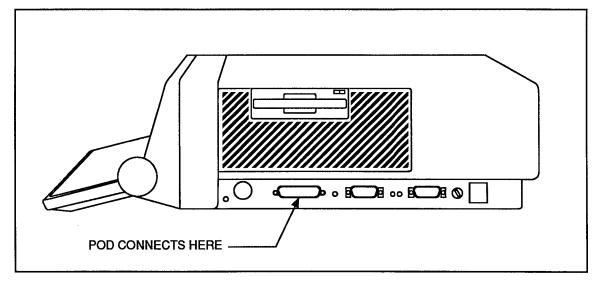

Before performing a Pod Self Test or using the Pod to troubleshoot a UUT, connect the Pod to the Mainframe as follows:

- 1. Check that the Mainframe is OFF.

- 2. Connect the Pod's round shielded cable to the Mainframe at the location shown in Figure 2-5. Secure the connector using the sliding collar.

Figure 2-5. Connection of the Interface Pod to the Mainframe

#### PERFORMING THE POD SELF TEST

2-10.

To perform the built-in self test on the Pod, use the following steps:

- 1. Make sure that the Pod is connected properly to the Mainframe.

- 2. If the ROM Modules are connected to a UUT, release the ROM Module cables from the UUT's ROM sockets. Remove the UUT ROMs from the ROM Module sockets.

#### **NOTE**

You must remove the UUT boot ROMs from the ROM Module sockets for self test to work properly. Self test may indicate an error if the UUT ROMs are not removed.

- 3. If the Sync Module is connected to a UUT, disconnect the Sync Module from the UUT.

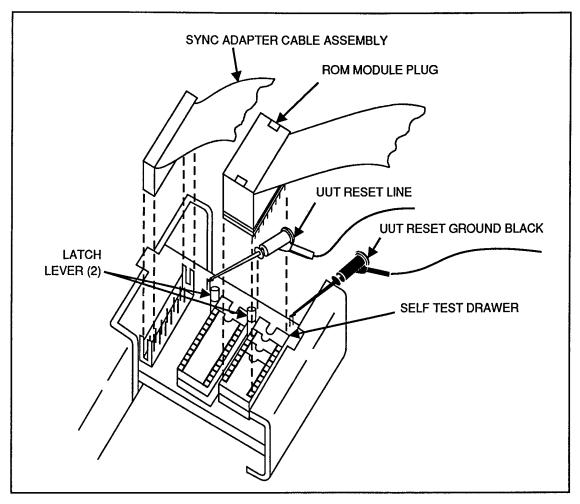

- 4. Open the self test socket drawer on the right-hand side of the Pod.

- 5. Insert the Sync Module Adapter Board cable into the socket on the self test pca (as shown in Figure 2-6). Connect the UUT Reset line flying lead to the reset line test connector and the UUT Reset ground line flying lead to the ground line test connector on the self test pca. (The Sync Module Reset ground line flying lead must be disconnected from the UUT during self test, otherwise an error will occur.)

#### **NOTE**

The Sync Module Self Test requires the use of the Sync Adapter cable assembly (Fluke part number 761684). If this cable assembly is not used with your UUT, unplug what you are now using and replace it with the Sync Adapter cable assembly.

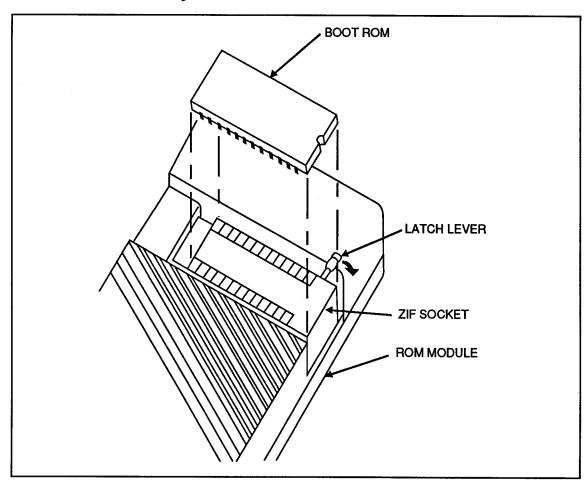

- 6. Insert the ROM Module cable plug into the Zero-Insertion Force (ZIF) self test socket (as shown in Figure 2-6):

- a. Open the ZIF socket by moving the latch lever to the vertical position.

- b. Insert the pins of the ROM Module cable plug into the ZIF socket. If you are using the 24-pin, 28-pin, or 32-pin ROM Module, insert the cable plug into the 32-pin socket. If you are using the 40-pin ROM Module, insert the cable plug into the 40-pin socket. Ensure that pin 1 of the ROM Module cable plug is inserted into pin 1 of the ZIF socket for the corresponding size.

#### **NOTE**

Pin 1 for a 24-pin, 28-pin, and 32-pin ROM Module cable plug is indicated on the 32-pin ZIF socket. If the ROM Module cable plug is inserted incorrectly, self test cannot determine if a ROM Module is connected and displays an error message.

- c. Secure the ROM Module cable plug in place by pushing down the latch lever.

- 7. Begin the Pod self test. Press the Main Menu key on the Mainframe to obtain the display "MAIN: SELFTEST POD". Press the ENTER key.

When the Pod passes the self test, the Mainframe displays a message indicating the Pod is functioning correctly. If the Mainframe displays a message indicating the Pod has failed the self test, turn to Appendix F for an explanation of the failure codes.

Figure 2-6. Connecting the ROM and Sync Modules to the Self Test PCA

- 8. Remove the ROM Module from the Self Test Socket.

- 9. Repeat steps 6 through 8 for all the ROM Modules connected to the Pod.

#### CONNECTING THE POD TO THE UUT

2-11.

#### **WARNING**

TO PREVENT POSSIBLE HAZARDS TO THE OPERATOR OR DAMAGE TO THE UUT, DISCONNECT ALL HIGH-VOLTAGE POWER SUPPLIES, THERMAL ELEMENTS, MOTORS, OR MECHANICAL ACTUATORS THAT ARE CONTROLLED OR PROGRAMMED BY THE UUT MICROPROCESSOR BEFORE CONNECTING THE POD.

Connect the Pod to the UUT as follows:

1. Be sure that power is removed from the UUT.

- 2. Disconnect UUT analog outputs or potentially hazardous UUT peripheral devices as described in the previous warning.

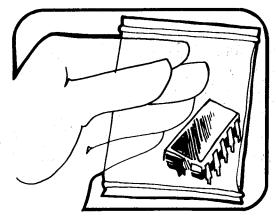

- 3. If necessary, disassemble the UUT to gain access to the ROM sockets. If the ROMs are still in the sockets, remove them. Place the ROMs into the ZIF sockets on the ROM Modules (ROM 1 into ROM Module 1, ROM 2 into ROM Module 2, etc.) as shown in Figure 2-7.

#### **CAUTION**

UUT power must be off when the UUT boot ROMs are removed from the UUT. Otherwise damage to the ROMs may occur.

#### **CAUTION**

The UUT boot ROMs must be plugged into the ROM Module sockets correctly or damage to the ROMs may occur.

Figure 2-7. Inserting UUT ROMs Into the ROM Module

#### **NOTE**

UUT data bits 24 through 31 correspond to ROM Module 1, data bits 16 through 23 to ROM Module 2, data bits 8 through 16 to ROM Module 3, and data bits 0 through 7 to ROM Module 4. If the UUT has an 8-bit boot ROM data bus, use only ROM Module 1. For a 16-bit boot ROM data bus, use ROM Modules 1 and 2. For a 32-bit boot ROM data bus, use ROM Modules 1, 2, 3, and 4.

4. Insert the ROM Modules into the UUT's ROM sockets and secure them (using the same means used to secure the ROMs). Make sure that pin 1 of the ROM Module plug is aligned with pin 1 of the ROM socket.

#### **CAUTION**

UUT power must be turned off before plugging the ROM Modules into the UUT boot ROM sockets or the UUT boot ROMs in the ROM Module sockets may be damaged.

#### NOTE

The ROM Module plug ends in an adapter that is easily damaged if not carefully inserted and removed from the UUT ROM sockets (a spare adapter is included with the ROM Module). Before testing, ensure an adequate supply of plug adapter replacements are available. The part is included in the List of Replacement Components in Section 1.

If the UUT uses soldered-in ROMs, see Appendix C of this manual, Testing UUTs With Soldered-in Components. A list of ROMs that can be replaced by the ROM Modules is contained in Appendix A of this manual.

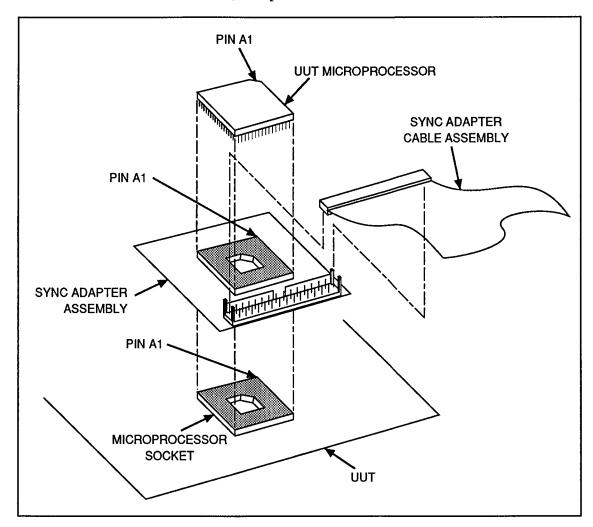

5. Connect the Sync Adapter assembly to the Sync Module (as shown in Figure 2-8). Remove the 68030 processor from the UUT and plug it into the socket on the adapter board. Connect the adapter board plug into the processor socket on the UUT. Connect the UUT RESET line (white wire) on the Sync Module to system reset on the UUT. Connect the UUT RESET ground line (black wire) to UUT ground.

#### **NOTE**

Connect the UUT RESET clip from the Sync Module to the UUT system reset line, **not** the RESET pin of the 68030 microprocessor. For more information about connecting the Sync Module RESET clip, see Appendix G.

The Sync Adapter assembly adapts the general design of the Sync Module to the processor-specific design of the UUT. In some cases, it may be necessary to design a different type of adapter board or test connector for a UUT. Table 2-1 contains a list of microprocessor signals and pin numbers for a typical adapter board connected to the Sync Adapter cable assembly. For a proper connection between the adapter board cable and the custom adapter board, use a 3M connector (part number 3494-2002) or equivalent.

Figure 2-8. Connecting the Sync Module to the UUT

If the UUT uses a soldered-in microprocessor, see Appendix C of this manual, Testing UUTs With Soldered-in Components.

#### **NOTE**

The Sync Module plug ends in an adapter that is easily damaged if not carefully inserted and removed from the UUT processor socket. Before testing, ensure an adequate supply of plug adapter replacements are available. The part is included in the List of Replacement Components in Section 1.

PIN PIN **NUMBER SIGNAL** NUMBER SIGNAL 1 **GND** D24 2 3 GND 4 D25 5 **GND** D26 6 7 **GND** 8 D27 9 **GND** 10 D28 **GND** 11 12 D29 13 **GND** D30 14 15 **GND** 16 D31 17 **GND** CLK 18 19 GND 20 RESET 21 GND 22  $\overline{\mathsf{AS}}$ 23 **GND** 24 BR  $\overline{\mathsf{B}\mathsf{G}}$ 25 **GND** 26 27 **GND** 28 **BGACK** 29 **GND** 30 HALT 31 **GND** 32 **STERM** 33 **GND** 34 (KEY)

**Table 2-1. Sync Adapter Signals**

6. Reassemble the UUT, using extender boards if necessary.

#### CAUTION

To prevent damage to the Pod, you must apply power to the Mainframe before turning the UUT power on. This activates protection circuits within the ROM Modules.

7. Apply power to the UUT.

POD SETUPS 2-12.

Since the Pod tests UUTs with a variety of different ROM types and number of boot ROMs, the unique features of each UUT must be described to the Pod (i.e., the characteristics of the UUT Reset, the type of ROM, the ROM data width, etc.). These attributes can be configured individually, or the Interactive Setup and Calibration routine can be used to configure the attributes automatically.

This section describes automatic configuration. Manual configuration is described in Appendix D for front panel operation and in Appendix E for TL/1 programming applications.

Use a known good UUT to set the attributes with the Interactive Setup and Calibration routine when making the first connection to a new type of UUT. Once the setups are verified with the known good UUT, the attributes should be saved so the setup values can later be restored to test and troubleshoot other UUTs of the same type.

#### **Interactive Setup and Calibration**

2-13.

To select the Interactive Setup and Calibration routine, press the POD key on the Mainframe keypad, select the SETUP softkey, and press ENTER.

Once the program has loaded, the Mainframe displays the following menu:

| Select de | sired | action | 1 : | <br>BUSY<br>STOPPED<br>RUN UUT                                   |  |

|-----------|-------|--------|-----|------------------------------------------------------------------|--|

| <b></b>   |       |        |     | STORING SEO<br>DISK ACCESS<br>MORE SOFT KEYS<br>MORE INFORMATION |  |

The INFO softkey contains information about the basic operation of the routine. First-time users are encouraged to read this information before continuing with the operation of the routine.

The Setup, Calibrate, and Check routines must be run in the correct order to ensure the Pod attributes are set correctly. (Once the Setup and Calibration routines are run, use the Check routine to verify that the Pod can communicate correctly with the UUT.)

Press the SETUP softkey to begin describing the physical makeup of your UUT to the Pod. (SETUP must be run before CALIBRT to ensure that the values under these routines are accurately set.) Setup runs through a series of questions that determine general information about the UUT, queries how the UUT is connected to the Pod, and verifies that the correct connections are made. These questions are presented in the following order:

1. Verify the UUT communications address (XFER\_ADR). UUT to Pod communications depend on one address on the UUT that is written to by the UUT. The transfer address can be set to any legal address as long as reads or writes to the address do not cause the UUT to halt or cause a bus exception. Each time data is communicated with the Pod, the UUT microprocessor reads and saves data from the specified address, transfers data to the Sync Module with a write cycle, then restores the original data with a second write cycle.

Pod accesses at the XFER\_ADR are made with supervisor data long bus cycles, and the address must be a multiple of 4.

If the transfer address is correct, press OK (F1). To change the transfer address, press CHANGE (F2), enter the new address, and press ENTER. The new address is then confirmed.

2. Verify the UUT boot ROM type (ROM\_TYPE).

If the UUT boot ROM type is correct, press OK (F1). To change the ROM type, press CHANGE (F2) and select the new type. If your UUT ROM type is not shown on the display, select OTHER and use the information contained in Appendix A of this manual to set the ROM description number.

3. Verify the number of ROM Modules (ROM\_MODS) connected to the UUT. UUTs tested by the Pod can have boot ROM with bus sizes that vary from design to design. A byte-wide boot ROM requires one ROM Module, a word-wide boot ROM requires two ROM Modules, and a longword-wide boot ROM requires four ROM Modules.

If the number of ROM Modules is correct, press OK (F1). To change the number of ROM Modules, press CHANGE (F2) and select the new number. The new number is then confirmed.

4. Verify that the ROM Module(s) are connected to the UUT boot ROM sockets. If the UUT has soldered in boot ROMs, see Appendix C.

After the ROM Modules are connected, press OK (F1).

If the correct order of ROM Modules cannot be determined, connect the ROM Modules in any order (the order is verified during Steps 11 and 12.)

5. Verify that the Sync Module is connected to the UUT (in most cases, the Sync Adapter assembly replaces the microprocessor in the UUT, which is placed in the socket on the Sync Adapter assembly). If the UUT has a soldered in microprocessor, see Appendix C.

After the Sync Module is connected, press OK (F1).

6. Verify that the RESET lead from the Sync Module is connected to the UUT (see Appendix G for information about where to connect the RESET lead to the UUT).

After the Sync Module RESET lead is connected, press OK (F1).

7. Verify the RESET pulse polarity (RST\_POL). This is the polarity that is asserted on the RESET lead from the Sync Module to the UUT. (Since the RESET lead is generally not connected directly to the UUT microprocessor, the connection polarity may differ from the RESET line of the microprocessor.)

If the RESET pulse polarity is correct, press OK (F1). To change the polarity, press CHANGE (F2) and select the correct polarity. The new RESET pulse polarity is then confirmed.

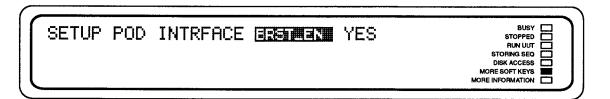

8. Verify the RESET pulse length (RST\_LEN). The Reset line on different UUTs may require different signal durations to reset the board successfully. This function allows you to select the length of the RESET signal (in microseconds) sent from the Pod to the UUT.

If the RESET pulse length is suitable, press OK (F1). To change the pulse length, press CHANGE (F2), enter the length of the pulse, and press ENTER. The new RESET pulse length is then confirmed.

- 9. Verify that power to the UUT is on by pressing OK (F1). During this step, the Pod performs a power sensing function at all the ROM Module connections. Press CONT (F1) to proceed to the next step.

- 10. Verify the RESET connection.

This step requires the use of the Mainframe probe. To verify the RESET connection, press OK (F1). You are asked to probe the RESET pin of the UUT microprocessor and then press the probe button. When the button is pressed, the Pod resets the UUT, which is detected by the probe. If the RESET pulse is determined to be incorrect, an error message is displayed. If the pulse is determined to be correct, the connection is confirmed.

To skip this check, press the SKIP (F2) softkey (skipping this step may be appropriate if the SETUP function has been previously executed and RESET verified at that time).

11. Automatically verifies the data path to ROM Module 1.

If the ROM Modules are connected to the wrong UUT ROM sockets, the error is detected and reported. Once the ROM Modules are reconnected, you are allowed to run the verification again. If for some reason ROM Module 1 cannot be identified with this step, the program continues to the next step.

12. Verify the remaining data paths to any other ROM Modules.

This step requires the use of the Mainframe probe. To verify the data paths to the ROM Module(s), press OK (F1). You are asked to probe a data line at the UUT microprocessor and then press the probe button. If Step 11 was unable to identify ROM Module 1, you are asked to probe D0. If ROM Module 1 was successfully identified in Step 11, you are asked to probe either D8, D16, or D24 (depending on the number of ROM Modules). If the data line you probe is determined to be incorrect (i.e., the ROM Module is in the wrong socket), an error is detected and reported. If the data line is determined to be correct, the connection is confirmed.

To skip this check, press the SKIP (F2) softkey.

13. The Setup routine is complete and a list of parameters that have been automatically set are displayed. Press ENTER/YES to return to the main menu.

Once the Setup routine has been completed, the Pod can now be calibrated to the UUT. Press CALIBRT (F3) to begin the Calibration routine. The Mainframe displays the following menu:

| CF | ALIBF | RATE: |      |         |          | BUSY<br>STOPPED<br>RUN UUT                                       |  |

|----|-------|-------|------|---------|----------|------------------------------------------------------------------|--|

|    | NFO.  |       | SYNE | RUNLUUT | MEINMENU | STORING SEO<br>DISK ACCESS<br>MORE SOFT KEYS<br>MORE INFORMATION |  |

The INFO softkey contains information about the operation of the options listed in this menu. First-time users should read this information before continuing with the operation of these options.

#### **NOTE**

BUS\_TEST (F2) must be run before RUN\_UUT (F4) to ensure accurate calibration.

BUS\_TEST (F2) is the first routine to use. This routine performs a series of steps that calibrate setup parameters that are required for Bus Test to interact properly with the UUT. These steps are presented in the following order:

- 1. Performs a series of tests on the UUT and automatically sets the bus cycle clock signal source (INTRFACE BCYCLCLK) and the ratio of boot ROM addresses accessed to boot ROM enables (INTRFACE BURST\_SZ).

- 2. Probe address line A3 at the UUT microprocessor with the Mainframe probe. Press the probe button. This allows the routine to set the number of bus cycles expected between UUT reset and the appearance of the stimulus address on the UUT address bus (CALIBTN ADR\_STIM) and specify the bus width in bytes at the microprocessor divided by the number of ROM Modules (CALIBTN CY\_SPLIT). Press ENTER/YES to continue to the next step.

- 3. Verifies that the Bus Test Calibrations are complete and that the routine is now ready to perform read/write sync pulse calibrations. Press ENTER/YES to return to the calibration menu.

SYNC (F3) is the next routine to perform. This routine calibrates the read/write sync pulses generated by the Pod during UUT accesses. Begin by probing A3 at the UUT microprocessor with the Mainframe probe. Press the probe button. The Pod performs a series of reads and writes to the UUT. Continue to hold the probe on A3 until the test concludes. Once the routine is finished, press CONT (F1) to return to the calibration menu.

#### **NOTE**

If the setup procedure fails during the SYNC routine, it may be due to UUT memory management circuit hardware that requires a different setup procedure. For more information, see the heading, Using the XFER\_CAL Setup, in Appendix D. Once the Transfer calibration has been changed, repeat the SYNC routine.

RUN\_UUT (F4) is the final calibration routine to perform. This routine automatically sets the number of microprocessor bus cycles expected between UUT reset and the fetch instruction at the RUN UUT starting address (CALIBRTN RUN\_UUT). Press CONT (F1) to return to the calibration menu.

To exit the calibration menu, press MAINMENU (F5).

Once the Setup and Calibration routines have been run, use CHECK (F4) to verify that the Pod can successfully interact with the UUT. Upon entering the Check routine, probe A3 of the UUT microprocessor with the Mainframe probe and press the probe button. As each test is performed, a pass or fail message is displayed. When the Check routine has run through the tests, a global pass or fail message is displayed. To return to the main menu, press CONT (F1). CHECK is also useful for confirming restored setups (those that were previously saved with the Mainframe SAVE SYSTEM SETTINGS).

To exit the Interactive Setup and Calibration routine, press QUIT (F5).

# Saving and Restoring Pod Setups

2-14.

Once the Pod setup and calibration information has been configured, use the SAVE SYSTEM function in the Setup Menu of the Mainframe to store the information in either a UUT file or on the Userdisk. To reload the information, use the RESTORE SYSTEM function in the Setup Menu of the Mainframe. For more information on the SAVE and RESTORE functions of the Mainframe, see the 9100-Series Technical User's Manual.

# **Setup for Relocated Boot ROM Address Space**

2-15.

Most UUTs have the boot ROM code located at the 68030 microprocessor's reset address. Some, however, have boot ROM relocated to a different region of memory. In such cases, the UUT boot address must be changed from the default value of 0. For more information, see the Appendix D heading, Using the 68030 ROM\_BASE Setup.

#### TROUBLESHOOTING HINTS

2-16.

When you begin testing, certain conditions on the UUT may cause the Pod to behave unpredictably. If this happens, check the following list to see if one of the conditions exists on your UUT (also see Appendix B, Problems Due to a Marginal UUT).

- Some UUTs may require various components to be initialized before the UUT can be successfully tested by the Pod (for instance, the dynamic RAM controller on the UUT may need to be initialized). You must determine what UUT components require initialization and the method for initializing these components.

- If the external cache system of the UUT overlays the UUT boot ROM area, the cache must be disabled for the Pod to operate correctly. If it is not disabled, the processor may fetch from the cache rather than the emulation memory in the Pod. The Pod will disable and enable processor-internal caches when necessary.

- Some UUTs may require the setup attributes to be changed in order for the UUT to function correctly. For more information on these setup attributes, see Appendix D.

- Ensure that the power supply voltage is at the correct level (in some cases an incorrect voltage may cause some tests to proceed correctly while others inexplicably fail).

- Watchdog timers and other circuits that can disrupt operation may need to be disabled.

| • |  |

|---|--|

# **Section 3**

# Pod Operations with 9100-Series Mainframes

# INTRODUCTION 3-1.

Once the Pod is connected to the Mainframe and UUT, testing of a 68030-based UUT can begin. This section describes the functions of the Pod and demonstrates how these functions operate while using the 9100-Series Mainframes. Also included in this section is a description of the 68030 processor signals.

## **NOTE**

TL/1 programming instructions for pod functions are described in 9100-Series Mainframe documentation except as noted in this section. Additional TL/1 descriptions are included in Appendix E of this manual.

Before you begin testing, you should be aware of the following notation conventions in this manual:

- For ease of reading, the two halves of the address are separated with a space in this manual (HHHH LLLL). However, do not try to enter addresses with a space. The Mainframe does not display addresses with a space.

- X denotes hex or binary digits, where the specific value may be any valid number. For example, the data value XX00 means that it is only important that the two least-significant digits are zero; the other two digits may be any value.

## **NOTE**

Whenever a function change is made to the values stored in the 9100-Series Digital Test System/Station, the new values are generally retained until the Test Station is either reset or power is turned off. In this manual, all the example displays show the default values for the If the Bus Test diagnostic routines do not detect a fault on the lines connected to the Sync Module, or if the symptoms are inconclusive, a further diagnostic step begins. If Bus Test first displays a fault message indicating the general nature of the UUT failure, press the CONT key to continue the diagnostic. Bus Test prompts you to measure activity on additional lines with the Mainframe probe. In some cases, the probe uses its enhanced capabilities to remeasure lines that are monitored by the Sync Module, providing new information to the Bus Test routine.

For example, in a UUT with the FC0 line stuck high, the following display may appear after the initial portion of the test:

| TEST BUS ROM1 C5 or OE is stuck invalid Press CONT to probe related lines | BUSY STOPPED S |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

After you press CONT, Bus Test prompts for the FC0 line to be probed:

At uP, Probe FCO, Pin D2

then Press Probe Button, or PROBE softkey

BIOSINI

MORE INFORMATION

Place the probe on the UUT line indicated by the Mainframe and press the probe button. If no fault is detected on that line, the Mainframe displays a message saying the line is OK. After a short time, the Mainframe displays another line to try. If, however, a fault is detected, the Mainframe beeps several times and prompts you to try the line again (in case you may not have made good contact with the line), as shown in the following display:

then Press Probe Button

BUSY | STOPPED | STOPPED | STOPPED | STORNOSEO | DISK ACCESS | MORE SOFT KEYS | MORE INFORMATION |

If the fault is detected again, the Mainframe beeps several times and a diagnostic fault condition message is displayed.

The Bus Test diagnostic routines continue to prompt you to test the data lines, status lines, and control lines of the microprocessor until a fault is found. If, for any reason, you choose to probe a different line than shown by the prompt, press the PROBE (F1) softkey. Since Bus Test checks UUT signals in groups (i.e., data, status, control) the signal you select after pressing the PROBE key must fall within the current group. Two softkeys, PREV and NEXT, allow you to scroll through the group of lines. To select the line you want to test, press the ENTER key.

As Bus Test progresses, faults are reported as they are encountered. After each fault message is displayed, press CONT on the Mainframe keypad to continue testing. Many times, related or additional faults are reported. If no other faults occur, the message "TEST BUS = FAILED" is displayed. Generally, the first fault reported is the primary fault, though other reported faults could have caused the primary fault. Continue testing until Bus Test reports all the faults it can find, then determine which is the primary fault and which are secondary effects.

To exit from the diagnostic routines once a fault message is displayed, press STOP.

#### **NOTE**

The Pod monitors power at the ROM Module connections to the UUT boot ROM sockets (power and ground pins on the UUT microprocessor are not monitored). If the UUT kernel is not functional because a power or ground line connected to any ROM Module is open, Bus Test detects and reports this condition.

# **Examples of Bus Test Operations and Fault Messages**

3-5.

The following examples are included to illustrate how Bus Test detects various faults. These fault diagnostic examples not only demonstrate simple fault messages, but also show how various signals of the 68030 microprocessor interact with other signals on the processor. In the latter case, the CONT key on the Mainframe keypad can be used to continue testing the UUT once an initial fault is found.

## Example 1: D24 tied to D25.

When TEST BUS is run, you are first prompted to probe various status and control lines. These lines could cause Bus Test failure symptoms similar to the data line faults and must be verified before the data lines are checked.

Upon completion of the probing, the data lines are automatically tested. Since these lines are among those monitored by the Sync Module, no probing is required to test them. When the fault is diagnosed, the following fault message is displayed:

| TEST BUS data line D24 pin M5 tied data line D25 pin N4 tied | BUSY STOPPED STORING SEO DISK ACCESS MORE SOFT KEYS MORE INFORMATION STORING SEO DISK ACCESS MORE SOFT KEYS MORE INFORMATION STORING SEO DISK ACCESS MORE SOFT KEYS DISK ACCESS MORE INFORMATION STORING SEO DISK ACCESS DISK |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

If CONT is pressed, Bus Test determines there are no further lines to test, so the following message is displayed:

TEST BUS = FAILED

BUSY | STOPPED | MORE SOFT KEYS | MORE INFORMATION |

This example demonstrates a Bus Test in which no additional faults are found after the initial fault message, indicating that the two shorted lines are the only problem.

Example 2: A31 shorted high (in a UUT that includes A31 in the Boot ROM decoding).

When TEST BUS is run, the following fault message is displayed:

| MORE INFORMATION | TEST BUS<br>forcing signs! "DSACKO pin F1 is active | BUSY<br>STOPPED<br>RINN UIT<br>STORING SEO<br>DISK ACCESS<br>MORE SOFT KEYS<br>MORE INFORMATION |  | $\int$ |

|------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--------|